By Doug Burger (opens in new tab), Distinguished Engineer, Microsoft

By Doug Burger (opens in new tab), Distinguished Engineer, Microsoft

Today at Hot Chips 2017 (opens in new tab), our cross-Microsoft team unveiled a new deep learning acceleration platform, codenamed Project Brainwave. I’m delighted to share more details in this post, since Project Brainwave achieves a major leap forward in both performance and flexibility for cloud-based serving of deep learning models. We designed the system for real-time AI, which means the system processes requests as fast as it receives them, with ultra-low latency. Real-time AI is becoming increasingly important as cloud infrastructures process live data streams, whether they be search queries, videos, sensor streams, or interactions with users.

The Project Brainwave system is built with three main layers:

- A high-performance, distributed system architecture;

- A hardware DNN engine synthesized onto FPGAs; and

- A compiler and runtime for low-friction deployment of trained models.

Spotlight: Blog post

First, Project Brainwave leverages the massive FPGA infrastructure (opens in new tab)that Microsoft has been deploying over the past few years. By attaching high-performance FPGAs directly to our datacenter network, we can serve DNNs as hardware microservices (opens in new tab), where a DNN can be mapped to a pool of remote FPGAs and called by a server with no software in the loop. This system architecture both reduces latency, since the CPU does not need to process incoming requests, and allows very high throughput, with the FPGA processing requests as fast as the network can stream them.

Second, Project Brainwave uses a powerful “soft” DNN processing unit (or DPU), synthesized onto commercially available FPGAs. A number of companies—both large companies and a slew of startups—are building hardened DPUs. Although some of these chips have high peak performance, they must choose their operators and data types at design time, which limits their flexibility. Project Brainwave takes a different approach, providing a design that scales across a range of data types, with the desired data type being a synthesis-time decision. The design combines both the ASIC digital signal processing blocks on the FPGAs and the synthesizable logic to provide a greater and more optimized number of functional units. This approach exploits the FPGA’s flexibility in two ways. First, we have defined highly customized, narrow-precision data types that increase performance without real losses in model accuracy. Second, we can incorporate research innovations into the hardware platform quickly (typically a few weeks), which is essential in this fast-moving space. As a result, we achieve performance comparable to – or greater than – many of these hard-coded DPU chips but are delivering the promised performance today.

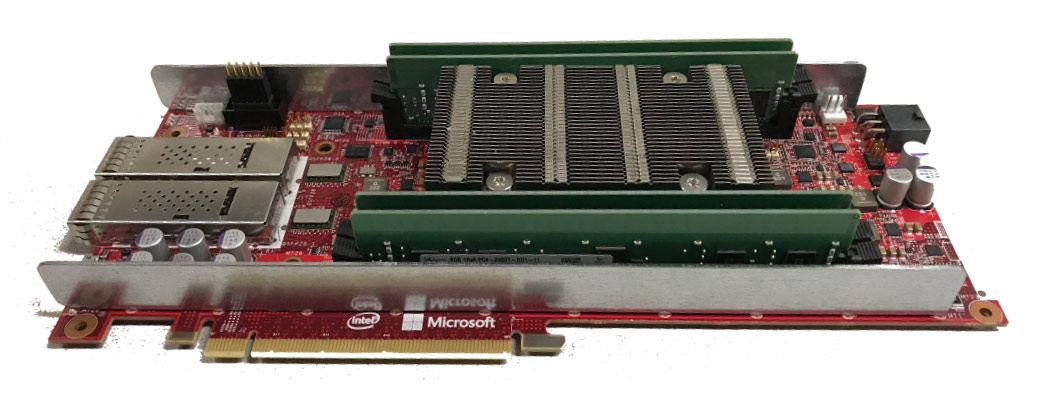

At Hot Chips, Project Brainwave was demonstrated using Intel’s new 14 nm Stratix 10 FPGA.

Third, Project Brainwave incorporates a software stack designed to support the wide range of popular deep learning frameworks. We already support Microsoft Cognitive Toolkit (opens in new tab) and Google’s Tensorflow (opens in new tab), and plan to support many others. We have defined a graph-based intermediate representation, to which we convert models trained in the popular frameworks, and then compile down to our high-performance infrastructure.

We architected this system to show high actual performance across a wide range of complex models, with batch-free execution. Companies and researchers building DNN accelerators often show performance demos using convolutional neural networks (CNNs). Since CNNs are so compute intensive, it is comparatively simple to achieve high performance numbers. Those results are often not representative of performance on more complex models from other domains, such as LSTMs or GRUs for natural language processing. Another technique that DNN processors often use to boost performance is running deep neural networks with high degrees of batching. While this technique is effective for throughput-based architectures—as well as off-line scenarios such as training—it is less effective for real-time AI. With large batches, the first query in a batch must wait for all of the many queries in the batch to complete. Our system, designed for real-time AI, can handle complex, memory-intensive models such as LSTMs (opens in new tab), without using batching to juice throughput.

At Hot Chips, Eric Chung (opens in new tab) and Jeremy Fowers (opens in new tab) demonstrated the Project Brainwave system ported to Intel’s new 14 nm Stratix 10 FPGA (opens in new tab). You can view the PowerPoint deck they presented at the event here (opens in new tab) (PDF file).

Even on early Stratix 10 silicon, the ported Project Brainwave system ran a large GRU model—five times larger than Resnet-50—with no batching, and achieved record-setting performance. The demo used Microsoft’s custom 8-bit floating point format (“ms-fp8”), which does not suffer accuracy losses (on average) across a range of models. We showed Stratix 10 sustaining 39.5 Teraflops on this large GRU, running each request in under one millisecond. At that level of performance, the Brainwave architecture sustains execution of over 130,000 compute operations per cycle, driven by one macro-instruction being issued each 10 cycles. Running on Stratix 10, Project Brainwave thus achieves unprecedented levels of demonstrated real-time AI performance on extremely challenging models. As we tune the system over the next few quarters, we expect significant further performance improvements.

We are working to bring this powerful, real-time AI system to users in Azure (opens in new tab), so that our customers can benefit from Project Brainwave directly, complementing the indirect access through our services such as Bing (opens in new tab). In the near future, we’ll detail when our Azure customers will be able to run their most complex deep learning models at record-setting performance. With the Project Brainwave system incorporated at scale and available to our customers, Microsoft Azure will have industry-leading capabilities for real-time AI.

Related:

- Accelerating Persistent Neural Networks at DataCenter Scale (opens in new tab)

- Inside the Microsoft FPGA-based configurable cloud (opens in new tab)

- Microsoft bets its future on a reprogrammable computer chip (opens in new tab)

- Follow Doug Burger on twitter (opens in new tab)